Research Area IV: High-Throughput Digital Signal Processing

To enable the highest bit rates for Teratronics, a massive signal processing performance is required. Since standard processors will not be able to meet this challenge in the near future, novel architectures and concepts are investigated in RA IV.

RA IV investigates novel architectures for high-speed optical communications and real-time handling of terabit/s data streams. Digital signal processing in teratronic systems cannot be accomplished by standard processors in the near future and requires novel, massively parallel architectures and concepts. These architectures and concepts are investigated in RA IV.

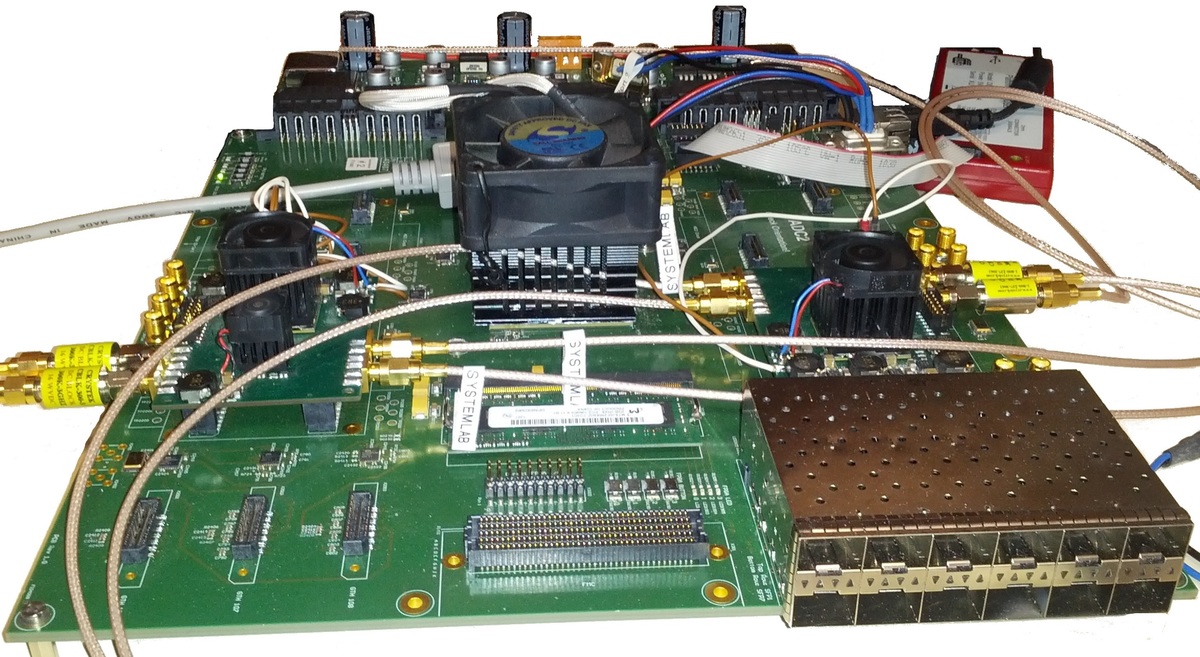

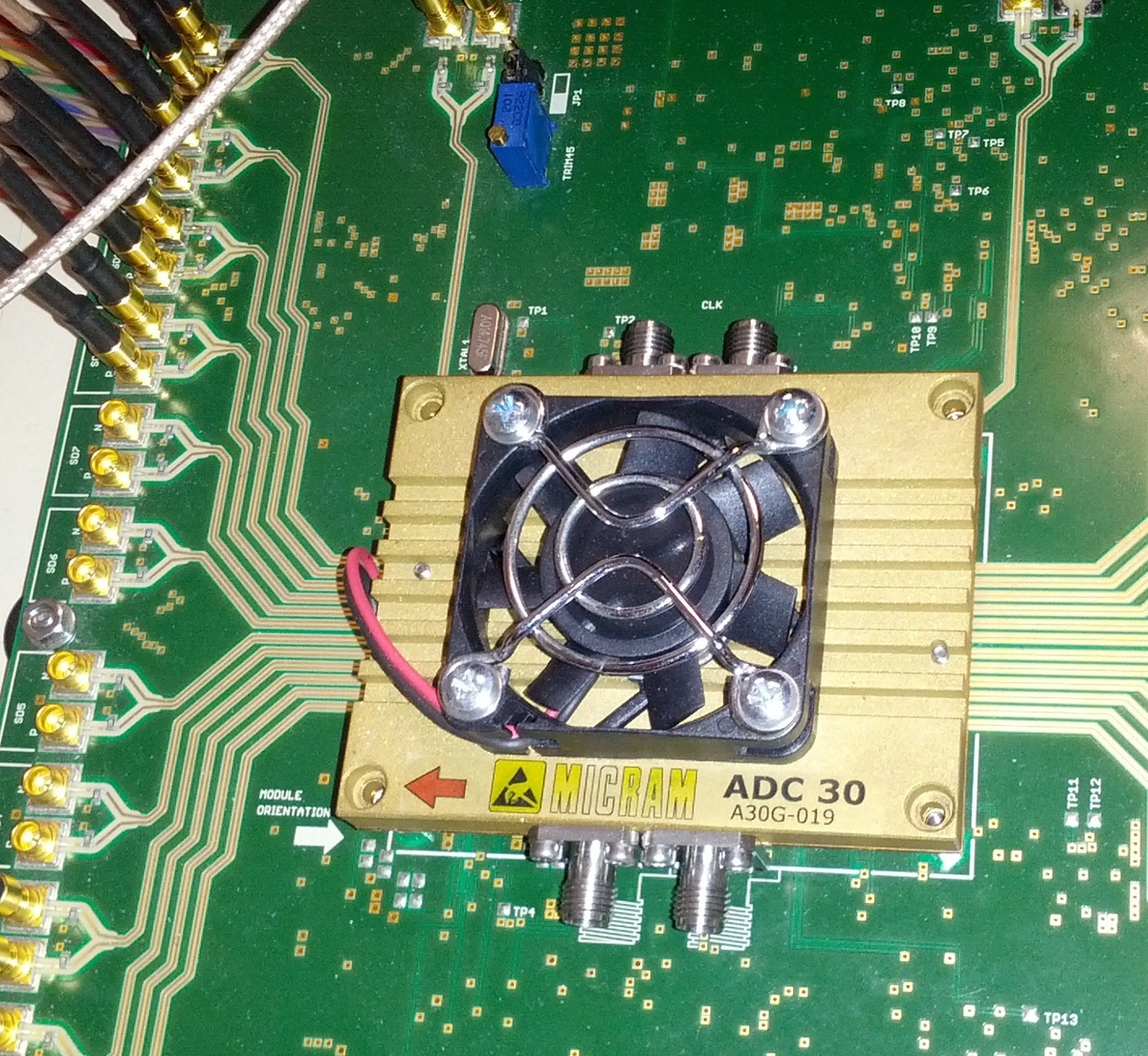

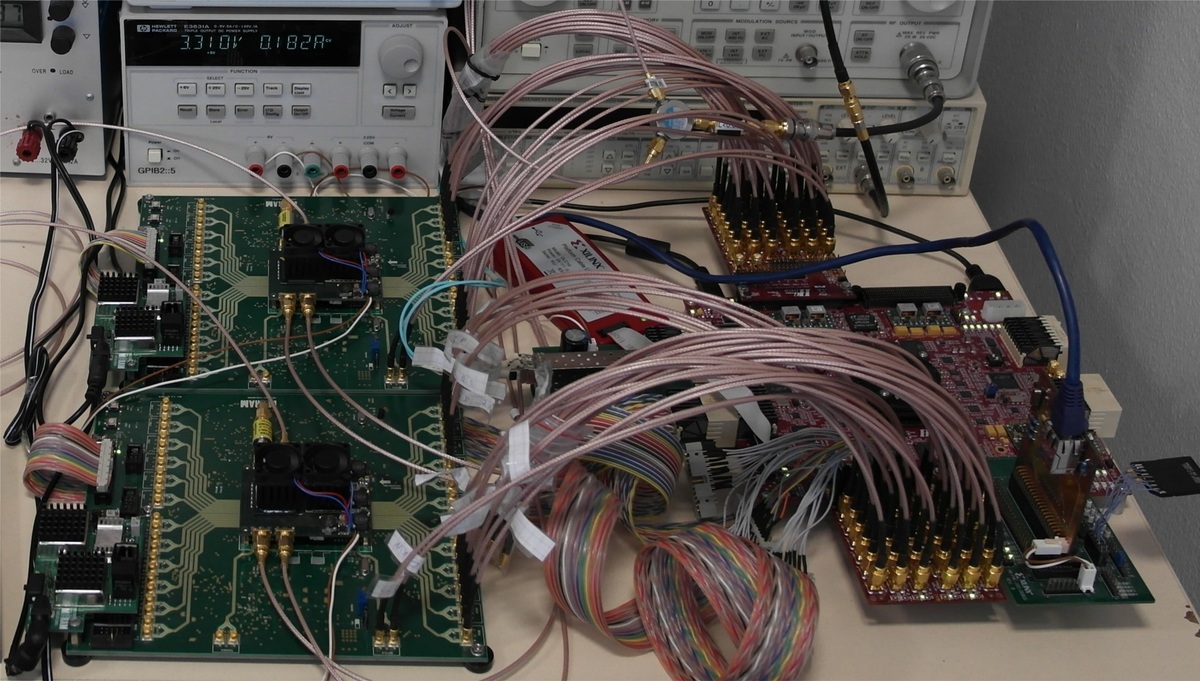

Utilizing the huge capabilities of state-of-the-art reconfigurable hardware systems, our work in RA IV uses custom-designed and optimized circuits to explore and analyze teratronic systems and their constraints. Deep understanding of field-programmable gate arrays (FPGA) allows low-level optimizations of special signal processing architectures that perform the required DSP tasks directly in dedicated hardware blocks. Reusable highly parametrized signal processing cores allow building up very fast systems that process multiple samples in parallel.

For future teratronic systems it will also become important, that a wide range of engineers are able to operate, program and adapt such systems, without having deepest digital system design knowledge. This is enabled by novel programming concepts and system architectures: Multiprocessor systems-on-chip based on application-specific processors achieve data rates beyond those of standard communication processors, but still provide programmability in high-level standard languages to enable and ease the deployment of such systems in interdisciplinary applications like teratronics. Combinations of specialized DSP cores and a more generic programmable multi-core system provide perfect flexibility and scalability. With relatively little adjustment of system parameters it is possible to create efficient systems operating at speeds of tens of gigasamples per second.

Participating Institutes and Research Groups

|

Institute of Information Processing Technology (ITIV)

|

|

Institute of Information Processing Technology (ITIV) |

.png) |

Chair of Dependable Nano Computing

|

|

Institute for Data Processing and Electronics (IPE)

|